The logic 1 at Q will not affect the logic 0 at the input to N2 as TG2, connected in opposite polarity to the CK and CK clock signals will be turned off. The logic 1 at Q will be inverted by N3 to become logic 0 at the Q output. When CK is logic 1 and CK is logic 0, TG1 will conduct and the logic 0 from D will be inverted by N2, so the output Qwill become logic 1. Initially, assuming that the CK and D are both at logic 0, CK will be at logic 1, so transmission gate TG1 will be in its high impedance state, preventing D from having any effect upon the flip-flop. The inverter N1 and the Buffer B1 create clock pulses CK and inverted clock pulses CK, which (because N1 and B1 have identical propagation delays), will exactly coincide in time when applied to the transmission gates of the flip-flop circuit. Apart from the NOT gate (N1) and the buffer (B1) controlling the CK input, the basic flip-flop uses only two NOT gates (N2 and N3) and two transmission gates (TG1 and TG2). 5.5.2 Basic CMOS Flip-flop Circuit CMOS Flip-flopįig 5.5.2 shows a basic circuit for a single flip-flop, which operates as a level triggered D Type flip-flop. In the absence of these pulse voltages however, or if they are reversed, with CK applied to the PMOS gate and CK applied to the NMOS gate, the conduction channel will exhibit an extremely high impedance (1 x 10 12Ω), virtually open circuit.įig. When the CK pulse is applied to the gate of the NMOS transistor and the CK to the PMOS transistor gate, the signal channel between the input and output terminal will conduct, and have a typical resistance of about 125O. The switching signal in digital circuits is provided by the clock pulses CK and CK. Signals, either digital or analogue, can pass between source and drain of these transistors in either direction when they are made to conduct by placing an appropriate voltage on the gate terminal of each transistor. In a transmission gate this is because the signal path is via two metal oxide silicon (MOS) transistors, one of which is PMOS and the other is NMOS, connected in parallel. Like a relay, once it is energised, information can flow through the switch in either direction, therefore the signal terminals are dual purpose and can be labelled in/out and out/in. 5.5.1(a) illustrates the basic structure of a transmission gate, which in some ways operates in a similar way to an electro-mechanical relay switch, except that it is much faster and very much smaller. The flip flops in CMOS ICs depend on a different type of gate, called a ‘Transmission Gate’ or ‘Bi-lateral Switch’, which make it possible to construct bi-stable flip-flops using less space within the IC, and have simpler structures than those used in TTL ICs.įig.

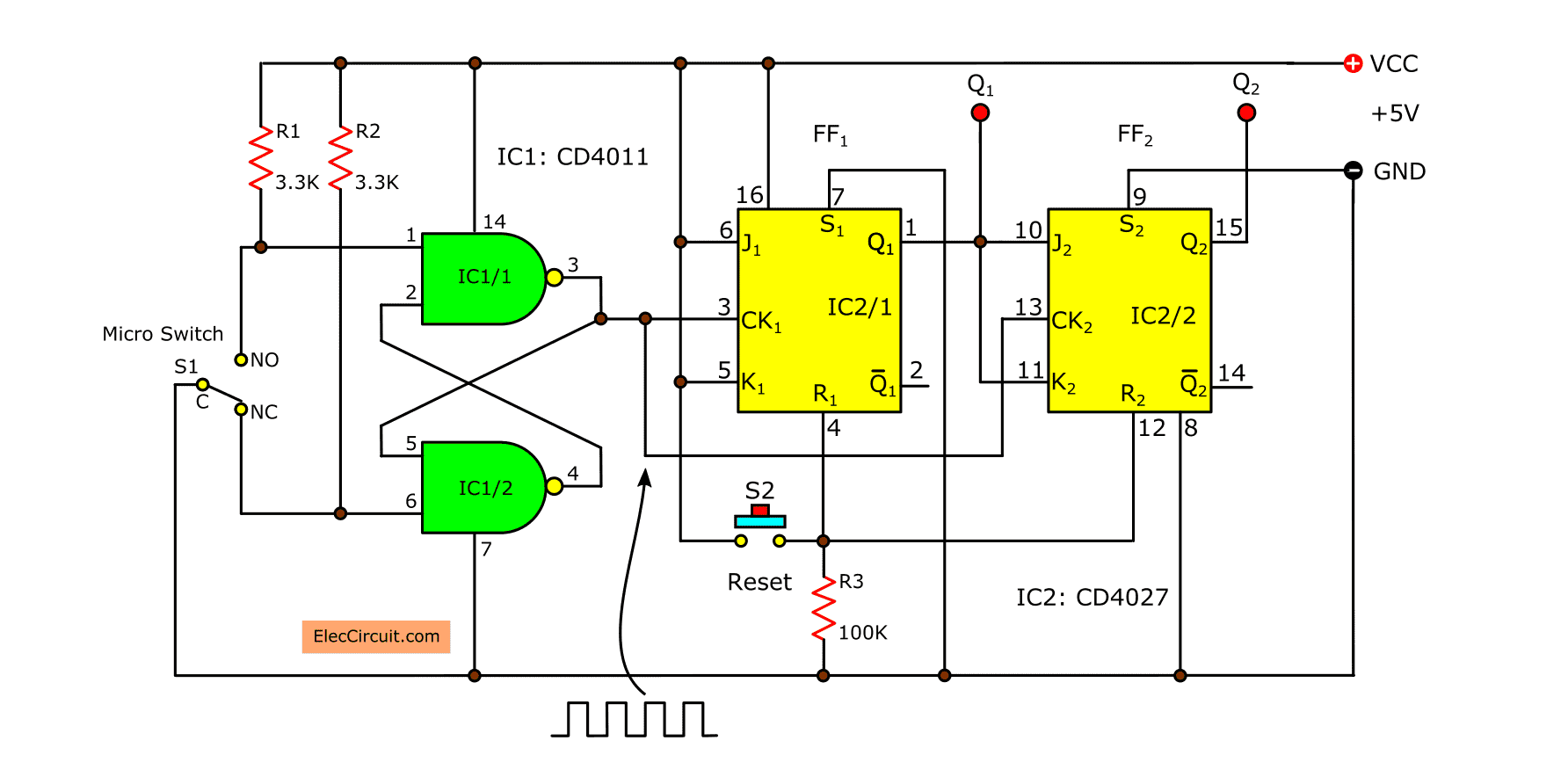

#Jk flip flop transistor schematic series

The flip-flops described so far in this module have been based on TTL technology, however many modern devices such as the 74HC and 74HCT series are CMOS ICs, which have radically different internal structures.

5.5.1 The CMOS Transmission Gate CMOS Transmission Gates

0 kommentar(er)

0 kommentar(er)